基于ADI及Intel FPGA的 JESD204C 介绍

【时间:2024 年 05 月 29 日, 来源:Cytech Engineer, 作者:Derek Xu】

一、 JESD204C 概述

模拟世界和数字世界之间的联系离不开ADC和DAC。随着人们数据需求的增加、频谱资源的紧缺,许多行业的数据密集型应用持续突破模数数据交互的界限。高速ADC/DAC,以及适合处理大数据的FPGA平台逐渐被开发出来。用于大带宽、高速的模/数、数/模数据传输的JESD204协议也应运而生。协议目前有JESD204A、JESD204B几个不的同版本,相比传统的LVDS传输方式,其链路速率更高,同时也节约IO数量。

JESD协议不同版本区别如下图(图1):

| 功能 | LVDS | JESD204A | JESD204B | JESD204C |

|---|---|---|---|---|

| Specification | 2001 | 2006 | 2011 | 2017 |

| Lane rate(max) | 1.0Gbps | 3.125Gbps | 12.5Gbps | 32Gbps |

| Multiple lanes | no | yes | yes | yes |

| Lane sync | no | yes | yes | yes |

| Multidevice sync | no | yes | yes | yes |

| Deterministic lattency | no | no | yes | yes |

| Harmonic clocking | no | no | yes | yes |

图1、JESD特性图

JESD204C的优点

- 减少PCB布板空间

- 减小器件的引脚和封装大小

- 更简单的时序控制

- 不用担心信道偏移

为满足未来数据密集型应用更快处理数据的需求,JESD204C被定义为数据转换器和逻辑器件之间必需的通信通道,高达32 GSPS的通道速率,64b/66b编码使超高带宽应用,能以最小的开销来提高系统效率。JESD204C的改进对5G通信、 B5G、6G通信系统、气象雷达和电子对抗、先进的仪器仪表和其他应用都大有裨益。

二、JESD204C 新术语

JESD204C引入了几个新术语和配置参数,主要用于描述与64b/66b和64b/80b链路层相关的功能。下图(图2)列出了最新相关的一些术语和参数,以及对每个术语和参数的简要说明。

| 术语 | 定义 |

|---|---|

| 块 | 一种结构,开头是一个2位同步报头,总共包含66或80个(BkW)位 |

| BkW | 块宽;一个块中的位数 |

| CMD | 命令,与命令通道相关 |

| 命令通道 | 使用同步报头提供的额外带宽的数据流 |

| E | 一个扩展多块中的多块数量 |

| EMB_LOCK | 声明扩展多块已对齐的一种状态 |

| EoEMB | 扩展多块结束标识符 |

| EoMB | 多块结束标识序列(00001);也称为导频信号 |

| 扩展多块 | 包含一个或多个多块的一组数据 |

| FEC | 前向纠错 |

| 填充位 | 一个用于在64b/80b编码模式中扩展块大小的人为填充位 |

| LEMC | 本地扩展多块时钟 |

| 多块 | 包含32个块的一组数据 |

| PCS | 物理编码子层 |

| SH | 同步报头 |

| SH_LOCK | 声明同步报头已对齐的一种状态d |

| 同步报头 | 块头最开始的两数据位,要保证数据位之间有变化 |

图2、JESD204C新术语图

三、JESD204C与JESD204B的变化

JESD204C传输层与JESD204B无异,但物理层发生了相当大的变化,具体阐述如下:

传输层:JESD204C的传输层与JESD204B相同。传输层中组装的数据帧以8个八位字块的形式通过链路发送。由于64位编码方案本身的一些特性,在有些配置中,帧边界会不与块边界对齐,存在帧不是恰好包括8个八位字的可能。

数据链路层:JESD204标准先前版本中的8b/10b编码方案,包括使用SYNC~引脚和使用K.28字符进行同步、通道对齐、错误监控,作为向后兼容选项保持不变。但从长远来看,大多数应用可能会使用JESD204C中新增的64位编码方案中的一种。基于IEEE802.3的64b/66b编码方案能提供最高效率。虽然称其为编码方案,但实际上并没有任何编码(比如类似于8b/10b的编码)。该方案仅在64位有效载荷数据前添加了两个报头位。由于这种情况,必须进行加扰,以便保持直流平衡并确保有足够的数据变化,从而使得JESD204C接收器中的时钟和数据恢复(CDR)电路能够可靠地恢复时钟。此外还增加了64b/80b选项,其时钟比与8b/10b方案相同,而且允许使用前向纠错等新特性。两种64位编码方案都不兼容JESD204B中使用的8b/10b编码。

物理层:JESD204C已将通道速率上限提高到32Gbps,而早期版本中确定的312.5Mbps下限保持不变。JESD204B的上限为12.5Gbps。虽然并未严格禁止,但建议不要将8b/10b编码用于16Gbps以上的通道速率;对于6Gbps以下的通道速率,也建议不要使用64b方案。

前向纠错:为了实现在更高通道速率下提供更稳健链路的目标,JESD204C包含了FEC选项。

时钟和同步: JESD204C将保留使用JESD204B中定义的SYSREF和器件时钟。但是,当使用任一种64位编码方案时,SYSREF不是对齐LMFC,而是用于对齐本地扩展多块时钟(LEMC),以提供一种实现确定性延迟和多芯片同步的机制。

64位编码方案的同步过程与JESD204B中使用的完全不同。SYNC信号已被去掉,同步初始化和错误报告现在将在应用层软件中处理。因此,新版本没有码组同步(CGS)或初始通道对齐序列(ILAS)。同步报头同步、扩展多块同步和扩展多块对齐是与同步相关的用于描述同步过程的新术语。这些同步阶段中的每一个都是使用32位同步字实现。

确定性延迟和多芯片同步:实现确定性延迟和多芯片同步的机制大部分与JESD204B相同。当使用64位编码方案中的一种时,没有子类2选项,仅支持子类1操作,SYSREF信号用于对齐JESD204子系统中所有器件的LEMC。

四、ADI、Intel FPGA 对JESD204C的器件支持

目前ADI、Intel公司都已经有了具体的器件对JESD204C支持,下图(图3):

| Device Family | JESD204C/B Protocol compatible | Key Features | |

|---|---|---|---|

| ADI | AD9081、AD9082、 AD9988、AD9986、 AD9177 | YES |

|

| Intel FPGA | Intel Agilex 系列 | NO | |

| Intel Stratix 10系列 | NO |

图3、相关器件说明图

五、JESD204C DEMO支持

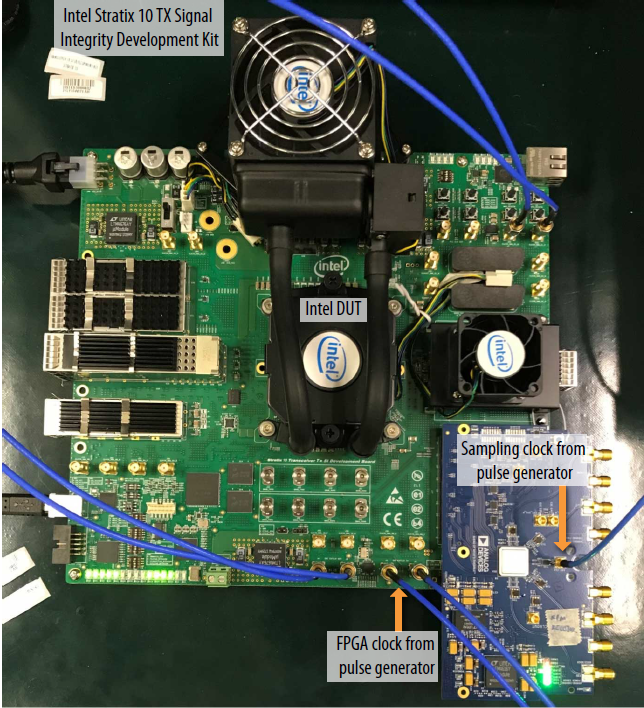

基于Intel FPGA 与ADI 相关器件对JESD204C的技术支持,骏龙科技相关的FAE会提供实物演示如下图(图4)所示,让您快速评估JESD204C的相关性能、掌握JESD204C的理论。

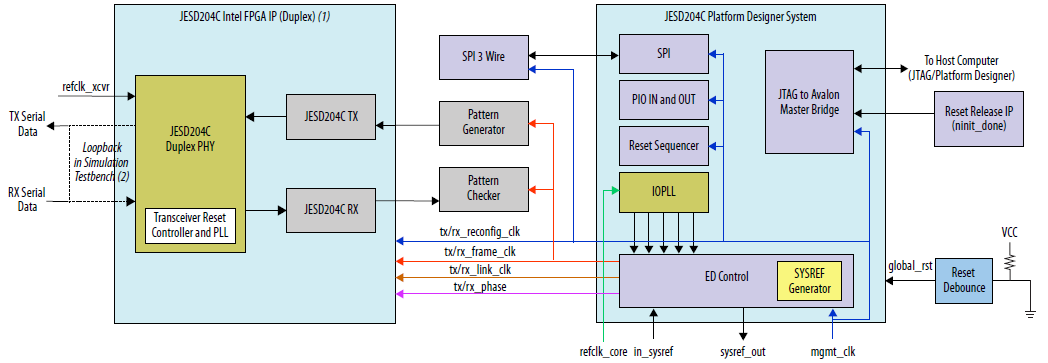

基于相关的DEMO,骏龙科技可以提供该设计的所有资料与相关的技术指导,包括工程搭建,如下图(图5)所示、仿真设计、板级工程测试、器件使用、JESD204C各种模式配置等。

六、总结

若您对JESD204C技术感兴趣,您可以点击下方「联系我们」,提交您的需求,我们骏龙科技公司愿意为您提供更详细的技术解答。

OPENCL设计基础

OPENCL设计基础