Intel FPGA Arria 10 SoC(上)- 硬件设计篇

【时间:2024 年 06 月 12 日, 来源:Cytech Engineer, 作者:Alvin Ma】

本文《Arria 10 SoC(上)- 硬件设计篇》为大家讲解从Quartus的参考工程开始,逐步介绍SoC器件的ARM端在FPGA内如何进项配置,搭建最小系统,能让ARM跑起来。在下一篇《Arria 10 SoC(下)- 软件启动设计篇》一文中,将讲述如何运用Quartus编译产生的文件来产生ARM的boot文件,以及简单的调试介绍。

对于Intel PSG的SoC类产品,许多人比较陌生,而SoC类产品,因为集成了ARM在内,功能比较全面;本篇介绍Arria 10 SoC 内FPGA侧的最小系统设计,直至ARM的Uboot引导成功,便于不了解Intel SoC类产品的工程师,快速上手,理解SoC的启动流程及最小系统搭建。Intel SoC FPGA的ARM侧设计,基于Qsys完成,在17.0之后的版本内,称之为Platform Design。

一、Intel SoC 最小系统

Intel针对每一代的器件的SoC都有一套完整的示例工程GSRD(Golden System Reference Design)。这其中提供了一组基本的硬件和软件系统组件,可以作为各种自定义用户设计的起点。

GHRD位于intelFPGA\18.1\embedded\examples\hardware。

注:该GSRD的外设所对应的是其官方开发板。以下链接为GHRD的详释。

我们骏龙科技针对Cyclone V与Arria 10两款FPGA,同样有对应的开发板。我们称之为Borax Module 以及 Silic SoC Module。该开发板对应资料都是公开的,如有需求,可与我们骏龙科技联系。

本篇的Boot Flow流程介绍基于GHRD开始。

二、Qsys的最小系统设计及介绍

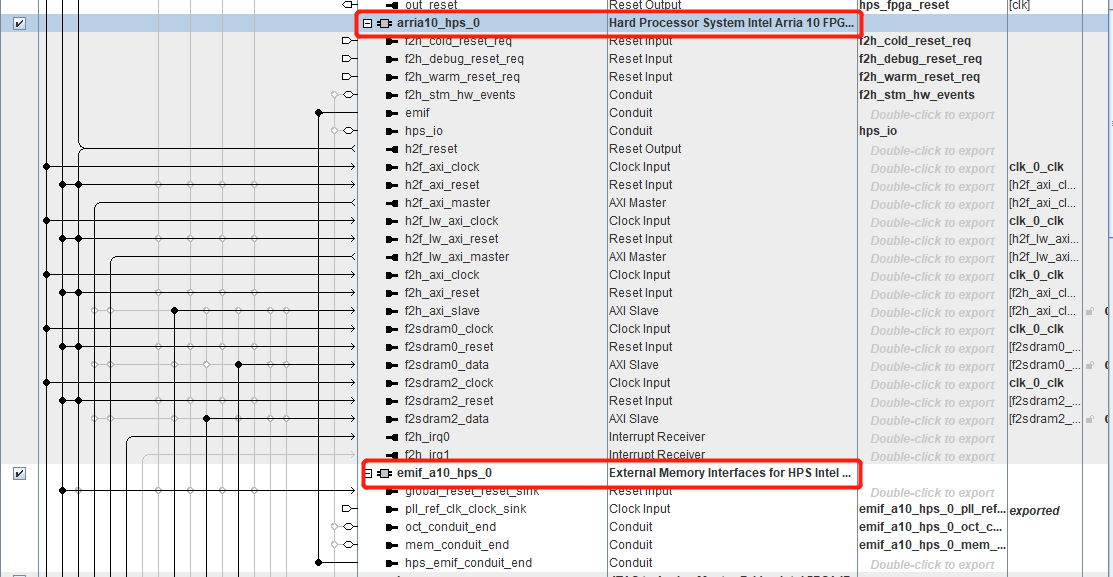

以Arria 10的GHRD为例,当打开ghrd_10as066n2.qsys后,其核心组件如下,其中包含A10的HPS组件以及ARM侧DDR的参数配置。该最小系统暂时不考虑交互模式,故不考虑时钟域问题。 ARM侧有专用的Pin提供时钟输入,范围为10~50Mhz。

Arria 10的HPS组件(Intel 将ARM侧称之为Hard Processor System) 打开HPS组件,如下:

分为FPGA Interface,HPS Clocks and Reset,Pin Mux and Peripherals,SDRAM四个子标签,每个子标签内有对应的配置内容。

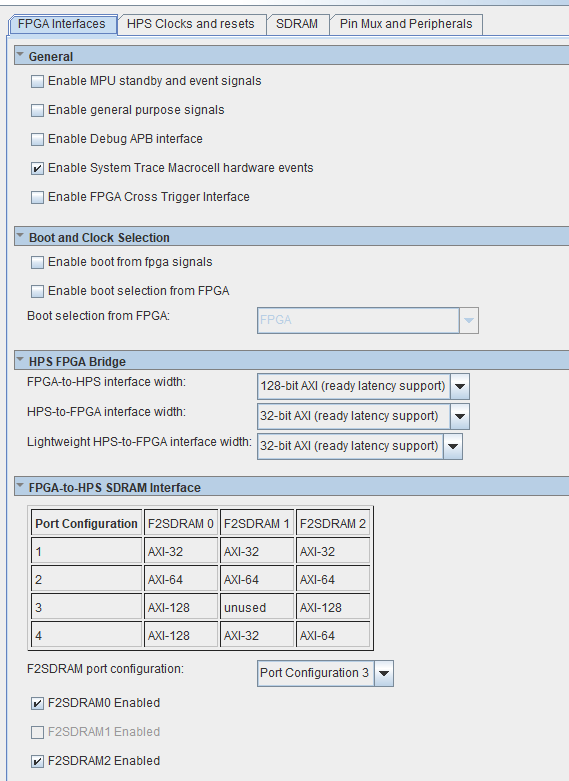

FPGA Interface

General

为一些通用设置,如使能一些信号以便调试使用,这其中用到的相对较少,可根据需求,自己选择,具体用法参考Hard Processor System Technical Reference Manual 手册内第27章节,有详细描述。

Boot and Clock Selection

Intel的SoC系列FPGA加载方式较为灵活,可从ARM侧引导,可从FPGA侧引导,也可分开各自引导。当您选择从FPGA加载时,需勾选Enable boot from FPGA signals以及 Enable boot selection from FPGA,以便引出boot信号与FPGA侧相连。

HPS FPGA Bridge

与FPGA侧交互的核心部分,该交互桥分为3种形式:

- FPGA:

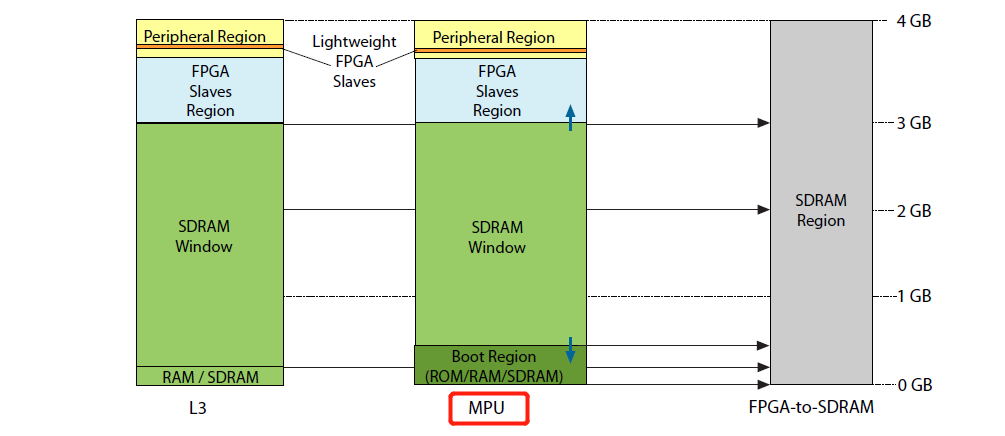

ARM的Bridge, 以FPGA作为Master,位宽从32bit-128bit可配,FPGA通过总线对ARM访问,因为Master是FPGA,故FPGA可访问所有地址区(0-FFFFFFFF,4G空间),使用该总线,操作需谨慎。

- ARM:

FPGA的Bridge,常用数据总线,位宽从32bit-128bit可配,作为ARM的外设存在,对FPGA进行访问。对于ARM而言,其外设地址为0xC0000000,长度为960M,在该地址后加上偏移量即ARM所看到的FPGA内模块的地址区。偏移量在Qsys组件内可定义。 比如,在Qsys内例化了一个On chip Memory,其使用的是FPGA的RAM资源,在Qsys内定义的地址区为100~3FFFF, 那么对于ARM而言,找到这个外设的地址为0xC0000000+100,结束地址为0xC003FFFF。

LW ARM - FPGA Bridge:

轻量级的外设桥,该桥仅32bit可配,外设入口地址为0xFF200000,容量为2M,常用于ARM与FPGA间的控制信号交互,如写FPGA侧寄存器,状态同步等。外设入口地址为0xFF200000,容量为2M,常用于ARM与FPGA间的控制信号交互,如写FPGA侧寄存器,状态同步等。

此处,后两个Bridge因为是以ARM作为Master, 而Cortex-A9的ARM(ARM-V7为 32bit处理器),其寻址空间仅为0-FFFFFFFF,所以分配给每一个外设的空间有限,如下图所示:

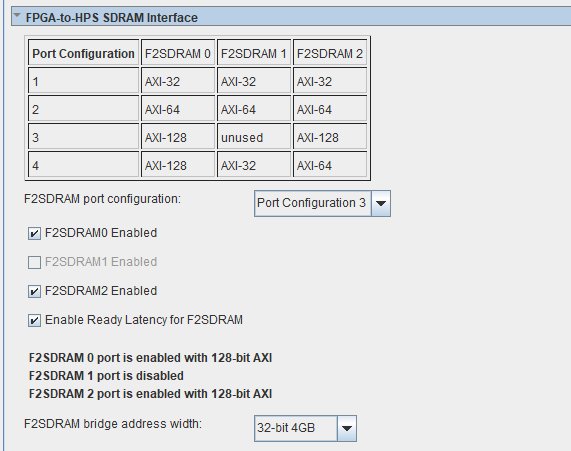

FPGA – HPS SDRAM Interface

这其实也是一个Bridge,用于FPGA访问ARM端的SDRAM。 这也是一种常用的数据交互方式,如,在ARM侧的SDRAM内开辟出某一空间段作为共享内存区(如1GB – 2GB空间段),FPGA可通过该接口将数据写入,当写完某一段数据后通知ARM读走。该方式适用于大数据量的交互,直接写到SDRAM内,不用通过L3总线桥接,效率较高,但数据的一致性,以及FPGA与ARM的读写速度比需要控制。(桥接方式由ACP接口来保证数据的一致性)

该桥有4种方式用于配置,可同时存在多个Port,如下:

后面的DMA, Security, Interrupt等,暂不在这份boot文档内多描述,有兴趣可以参考TRM手册使用。

HPS Clocks and Reset

Input Clocks :

该标签下,有一项较为重要的是External Clock Source, 该时钟为外部送入时钟,由使用者自定义的,常用为25M,范围为10-50M。

- Internal Clocks and Output Clocks:

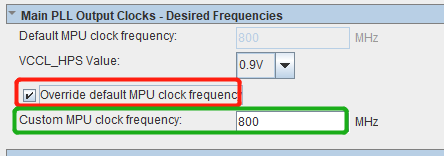

默认情况下,MPU的主频为当前芯片速度等级所支持的最大频率(-3/800M,-2/1G,-1/1.2G),若需调整MPU,可使能Override default MPU clock,如下图:

时钟设置完,在最下端,会有pll report的参数列,告知pll的参数配置,该配置会直接体现在handoff文件夹内的,hps.xml文件内,由他去影响uboot阶段的时钟初始化。

- Reset:

当使能FPGA-HPS warm/clod reset request时,会在fpga端产生相应的复位信号,即FPGA可控制ARM的冷热复位,常用于FPGA与ARM的系统级握手,也可作为人工定制的看门狗使用。

Pin Mux and Peripheral

该标签栏下有3个子标签,IP Selection, Advanced Pin and Placement, Advanced FPGA Placement。虽有3个子标签,但其产生的作用都是一样的,皆为ARM侧Pin脚的约束。

IP Selection

- 该标签下,根据所选择的IP,在apply后会自动去分配IO。

Advanced Pin and Placement

- 个人较为倾向于在该标签栏内设置,由于ARM的Pin脚是复用的,该标签内给出了17的专用IO以及48个共享IO的所有可能性,可灵活配置。

Advanced FPGA Placement

因为芯片是集FPGA与ARM为一体,所有两者的IO可以互相share,若当ARM侧的IO放不下时,可将部分IO放在FPGA的其他Bank上,常见如:第二路EMAC,其与Nand相冲突,当使用Nand时,可将其分配至FPGA侧。

注:当GPIO share时(share bank内arm不用的IO给FPGA用),是按照IO列分配的,一次性12个,不能将单独的某一个IO share。

SDRAM

SDRAM在物理上用的还是FPGA的DDR控制器,FPGA的DDR控制器存在于每个IO Bank上(这一点与Cyclone V不同)。所以在uboot加载时,需要先将FPGA的IO配置起来,否则,uboot阶段的校准无法完成(ARM侧DDR的参考时钟最好独立给)。

此处调用的IP名为 External Memory Interface for HPS,配置界面与FPGA侧的EMIF IP一致。

需要注意的是:ARM侧的DDR占用整个片子上的2K,2J两个Bank,受制于Arria 10 EMIF控制器的硬件约束,其所能使用的IO 共40bit,其中8bit作为ECC存在,故最大只能到32bit的DQ位宽。而且,ECC的bank 位置是固定的,不可随意调整,DQ组的顺序也有要求,这点跟FPGA不一样,FPGA内的DQ组与组之间可随意调整。从调试经验看,百分之八十的uboot起不来,Kernel无法正常引导都是由DDR异常造成的。

以上为SoC Qsys内最小系统设计,该系统已可正常引导uboot及kernel,其他接口可基于该系统自行添加。

三、总结

从上面的介绍中,可以看到当使用SoC芯片时,我们需要在Quartus工程内做一些关于ARM的配置,我们称之为最小系统,确保ARM可以正常跑起来,后续的扩展设计可基于该最小系统展开。如您对此还有疑问,可点击下方[联系我们],提交您的疑问,我们骏龙科技公司愿为您做更进一步的分析与答疑。

联系我们

OPENCL设计基础

OPENCL设计基础