Intel FPGA Arria 10 SoC(下)- 软件启动设计篇

【时间:2024 年 06 月 14 日, 来源:Cytech Engineer, 作者:Alvin Ma】

上一篇《Arria 10 SoC(上)- 硬件设计篇 》简单介绍了Arria 10 SoC FPGA在启动时,FPGA部分所需要的主要设计工作。本篇为下篇《Arria 10 SoC(下)- 软件启动设计篇》,将为大家讲述如何运用 Quartus 编译产生的文件来产生 ARM的boot文件,以及简单的调试介绍。

一、Uboot的产生

当 Qsys 最小系统完成后,在 Quartus工程内例化 Qsys 所产生的最小系统,然后编译整个Quaruts工程。

注:ARM方面分配的 IO 需在顶层定义 Input/Output,但不需要在 Pin Planner做管脚约束。

- 当编译完成后,在工程主目录下会生成 Handoff 文件夹,我们需使用该文件夹产生 Uboot。

- Arria 10系列与 Cyclone V系列不同之处在于 uboot的编译需放在 Linux系统下( Ubuntu, CentOS皆可)。

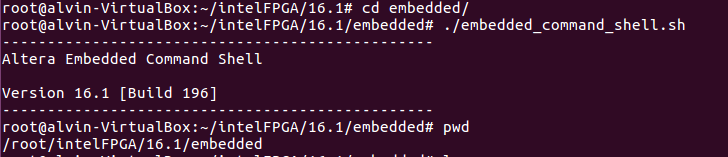

- 在 ~intelFPGA/16.1/embedded 下,执行 embedded_command_shell.sh 的脚本,输入 bsp-editor 命令,打开 uboot配置界面,如下:

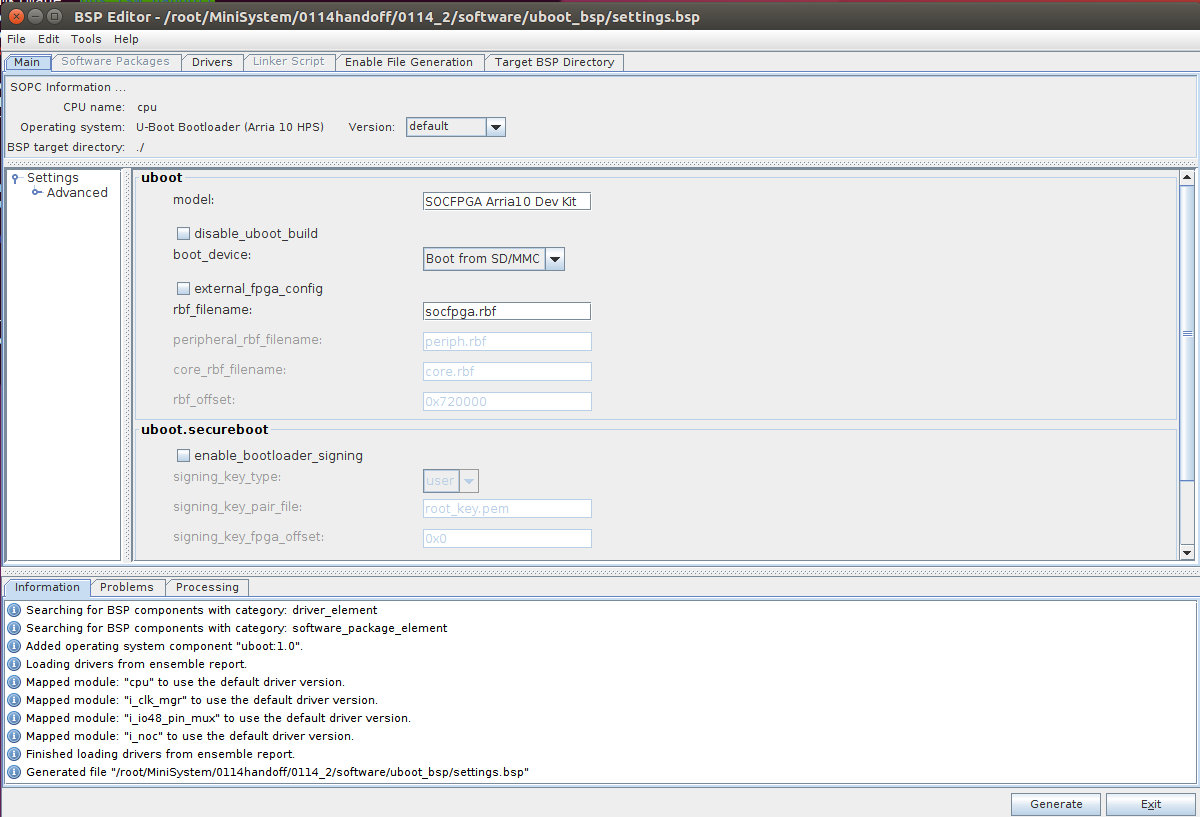

在File工具栏下,新建 bsp,路径指到 handoff 所在。如下:

注:external_fpga_config 在调试阶段是个很方便的手段,当使能该选项后,可以通过 Quartus工具内的 Programmer下载 sof文件以配置 FPGA。使能后,当boot代码执行到此处时,会等待外部 FPGA配置。 好处在于,Arria 10的 rbf文件相对较大,若存在Flash内由boot代码去加载,那每次烧写/擦除 QSPI Flash会浪费很多时间。

- 配置完成后,点击 Generate,此时,在相应的路径下会生成 software/uboot_spl 文件夹,该文件夹内存在一个 devicetree.dts 的文件。

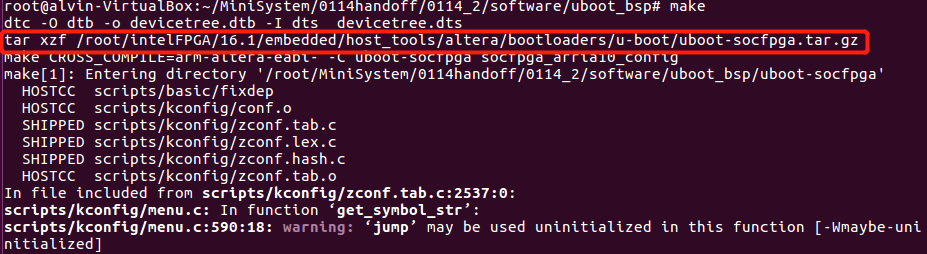

- 进入该文件夹内使用 make指令编译 uboot。

- 工具的安装路径下,存在压缩好的 uboot源码,从log可以看到,其第一件事会去解压 uboot源码,然后执行编译,具体的编译过程,有兴趣可以研究 Makefile文件。

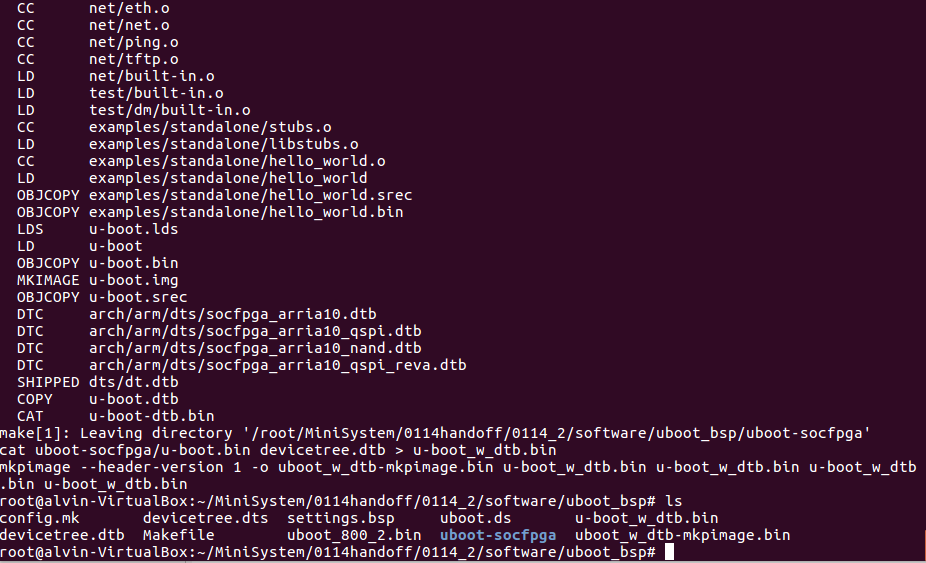

- Makefile 的规则是将 dts 文件编译成 dtb,然后与生成的 uboot.bin 与 devicetree.dtb 合成 u_boot_w_dtb.bin 文件,再通过 mkimage 工具给其加上头信息,产生 uboot_w_dtb-mkpimage.bin,该文件即为 SoC芯片的 uboot镜像文件,将其存入对应的配置器件内即可。

Linux下进行的第二件事,通过 mkimage 工具为所产生的 rbf文件加上头信息。如下:

mkimage -A arm -T firmware -C none -a 0 -e 0 -n "RBF" -d ./xxx.rbf ./xxx.rbf.mkimage

产生的 xxx.rbf.mkimage 文件即为 arm 在配置 FPGA 时所需要的 FPGA 配置文件。

二、Uboot的调试

标准的boot log如下:

- CPU: Altera SOCFPGA Arria 10 Platform

- BOARD: Altera SOCFPGA Arria 10 Dev Kit

- I2C: ready

- DRAM: WARNING: Caches not enabled

- SF: Read data capture delay calibrated to 3 (0 - 6)

- SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

- Full Configuration Succeeded.

- SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

- DDRCAL: Success

- INFO: Skip relocation as SDRAM is non secure memory

- Reserving 2048 Bytes for IRQ stack at: ffe346e8

- DRAM: 2 GiB

- WARNING: Caches not enabled

- SF: Read data capture delay calibrated to 8 (0 - 15)

- SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

*** Warning: bad CRC, using default environment

- In: serial

- Out: serial

- Err: serial

- Model: SOCFPGA Arria10 Dev Kit

- Net: Phy not found

- dwmac.ff800000

- Hit any key to stop autoboot: 0

注意几处:

A. Full Configuration Succeeded 标志着 FPGA的配置完成,使用的是全配置模式,同样,有 early release mode,意味着在uboot阶段仅加载FPGA的SDRAM 对应的IO,使得uboot能正常往下执行。

设置方式:

Quartus -> Device -> Device and Pin option -> General -> Option -> Enable the HPS early release of HPS IO.

B. DDRCAL: Success 标志着 SDRAM 校准通过,若此处打印 DDRCLK: Fail,相对应的log会输出resetting 的 log 信息,并且 log 不断循环。

这两处是经常导致 uboot无法正常引导的因素。

注: 因为Intel所提供的 uboot源码,在硬件上对应其相应的开发板,举个例子,如 EMAC的 PHY,Intel开发板使用 KSZ9031,若您的设计中PHY型号不匹配,需在 uboot源码内修改相应的 PHY驱动,否则在 uboot 下将无法使用网口。

Uboot的调试手段

调试手段千变万化,可根据现象相应调整,这里建议两种方式:

1. 若您对 uboot源码足够了解,可根据 log输出的信息,到对应代码处加打印,定位具体问题点。

2. 若您对 uboot源码接触不多,建议您使用 Eclipse工具调试。

Eclipse的调试方式

DS-5是 ARM所提供的开发工具,在 socEDS 安装完成后(按照路径下有 embedded文件夹),会自动询问您是否安装 DS-5。

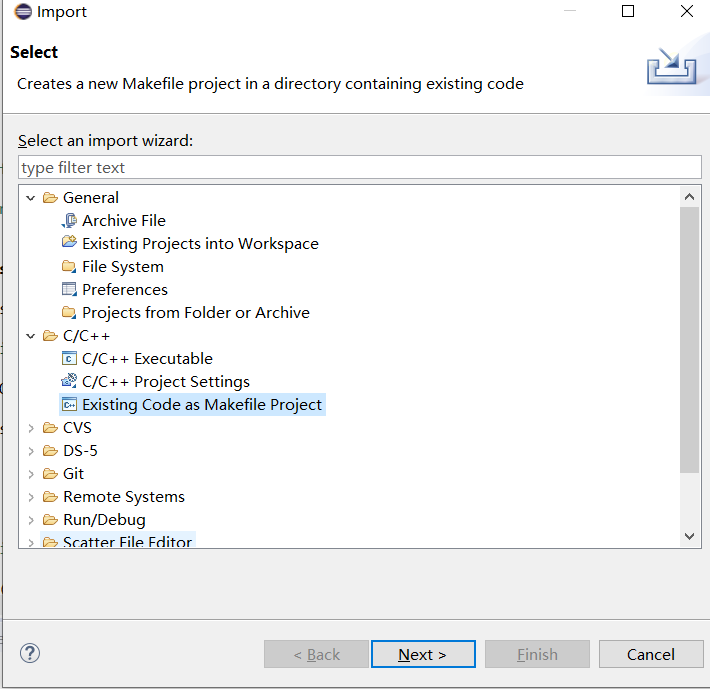

打开 DS-5, 使用import选项将进的 uboot源码导入到工程内,如下:

使用 Existing Code as Makefile Project, 然后切换至对应的路径处。

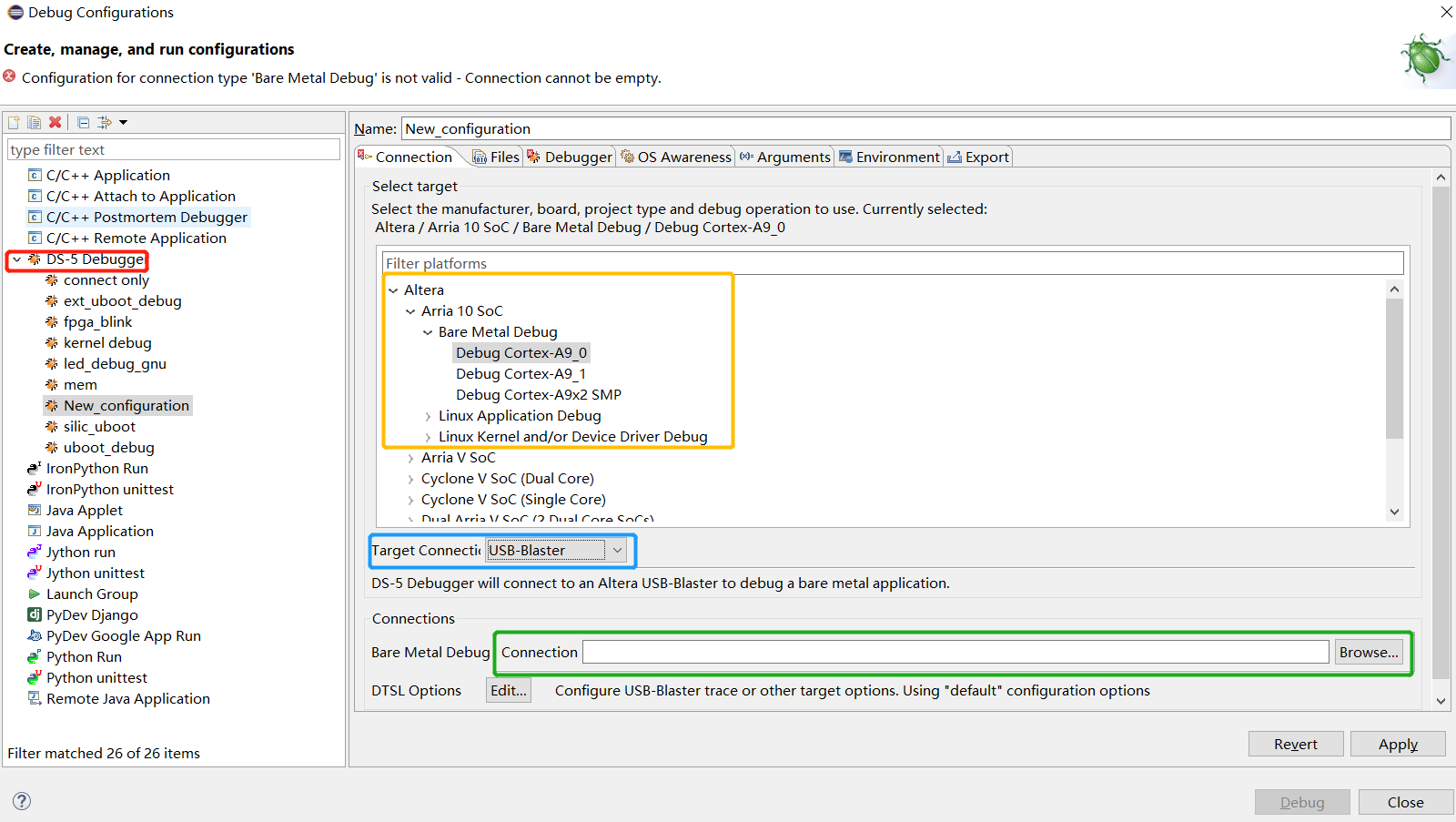

- 红色框:双击 DS-5 Debugger,新建调试标签页,新建名为New_configuration,可自由修改。

- 黄色框: 选择对应的器件,此外,根据自己应用情况,选择模式,uboot是 Bare Metal的一种。

- 蓝色框:选择调试介质,使用FPGA的下载器usb-blaster

- 绿色框:点开 Browse,选择对应的usb-blaster设备

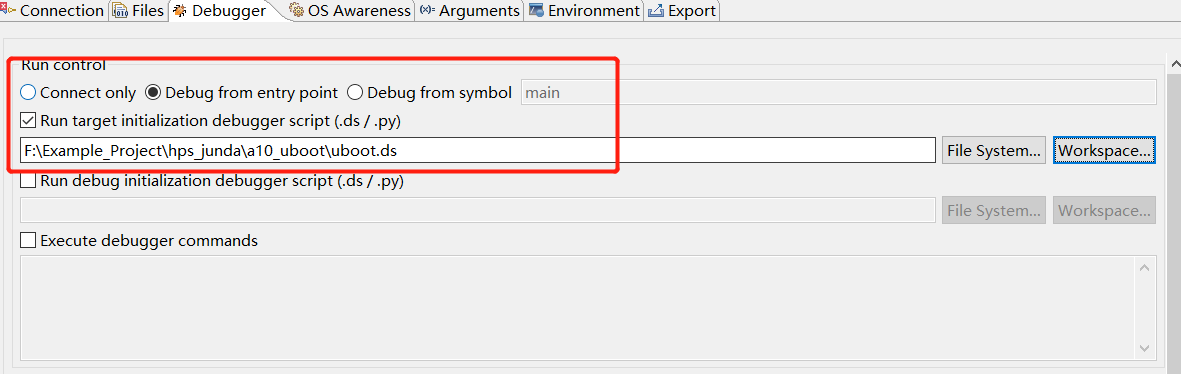

切换到debugger下

红色框:选择从断点处,开始调试,指明调试的ds文件

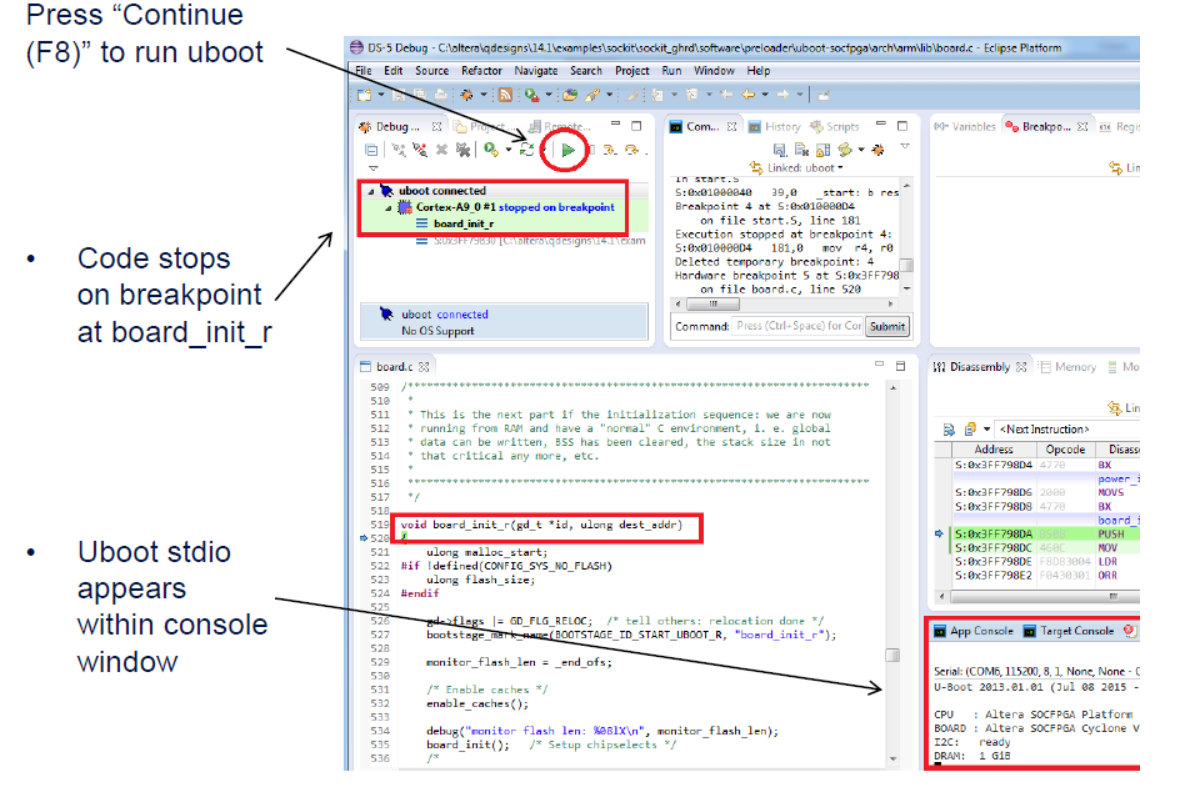

调试界面如下,F8为全执行,F5为单步执行,根据自身情况设置断点单步调试,定位问题具体问题所在。

三、总结

以上内容为整个 Arria 10 SoC 最小系统的设计流程,SoC类芯片因为将 FPGA + ARM 合在了同一个芯片中,从板子的面积,芯片的成本 以及系统的稳定性上都优于 FPGA+ARM 的分离设计方案。如您对此类芯片有更多的兴趣,可点击下方[联系我们],提交您的疑问,我们骏龙科技愿为您做更深入的讲解。

OPENCL设计基础

OPENCL设计基础